以太网通信硬件电路设计方案的集成电路设计探析

以太网作为现代有线网络通信的基石,其硬件电路设计方案的核心在于集成电路(IC)的设计与选型。一个高效、稳定且符合标准的以太网通信硬件电路,通常需要精心选择和设计多个关键集成电路模块。以下将系统阐述以太网通信硬件电路设计中涉及的集成电路设计方案。

一、 核心集成电路方案概述

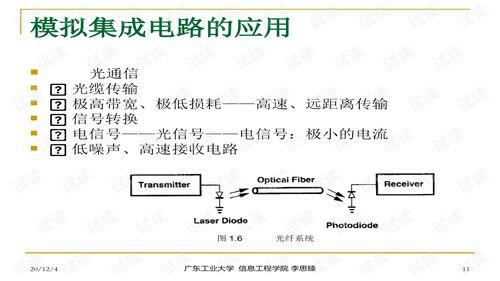

以太网硬件电路设计主要围绕物理层(PHY)和数据链路层的媒体访问控制(MAC)展开。现代方案通常将MAC集成在微处理器或FPGA中,而PHY层则需要独立的专用集成电路或集成在SoC中。

二、 关键集成电路模块设计方案

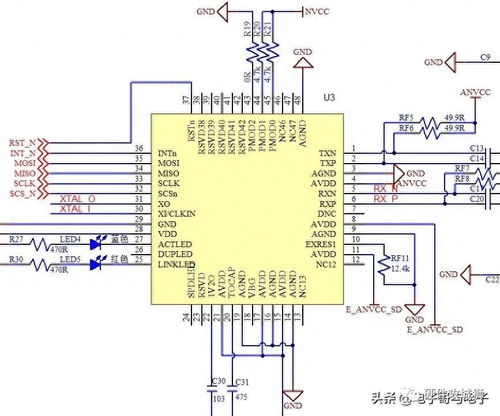

- 以太网PHY芯片设计/选型方案

- 功能:负责物理层信号的调制解调、编解码(如曼彻斯特编码、4B/5B编码)、时钟恢复、信号驱动与接收、链路检测(Auto-Negotiation)以及电气隔离(通过集成或外接变压器实现)。

- 设计考量:

- 接口标准:支持10/100/1000Mbps乃至更高(如2.5G/5G/10G)的速率,兼容IEEE 802.3系列标准。

- 接口类型:支持MII、RMII、GMII、RGMII、SGMII等MAC-PHY接口,需与主控制器匹配。

- 工艺与功耗:采用低功耗CMOS工艺,支持节能以太网(EEE)功能。

- 封装与集成度:常见QFN、LQFP封装,高级芯片可能集成变压器(如Marvell的LDO方案)或交换功能。

- 代表芯片系列:Microchip(原Microsemi)的LAN系列、Realtek的RTL系列、Broadcom的BCM系列、TI的DP系列等。

- 集成MAC的主控制器方案

- 方案选择:

- 微控制器/微处理器(MCU/MPU):许多现代MCU/MPU(如ST的STM32系列、NXP的i.MX系列、Microchip的SAM系列)内部集成了以太网MAC控制器,极大简化了外围电路设计。设计时需通过RGMII/MII等接口连接外部PHY芯片。

- FPGA/SoC:在高速、定制化要求高的场合,可在FPGA(如Xilinx的Zynq、Intel的Cyclone V SoC)内部利用IP核(如Tri-Speed Ethernet MAC IP)实现MAC功能,并与内部处理器或外部PHY对接,提供极高的灵活性。

- 磁性元件(网络变压器)与接口电路

- 虽然磁性元件本身不是硅基IC,但其接口保护电路常与PHY设计协同考虑。部分先进PHY芯片采用“变压器共模扼流圈集成”或“PoE(以太网供电)集成”方案,减少了外围元件数量。PoE受电设备(PD)控制器IC(如TI的TPS系列)也是重要的配套集成电路。

- 电源管理集成电路(PMIC)

- 以太网电路通常需要多个电压轨(如PHY芯片的1.2V、2.5V、3.3V等)。采用高效率、低噪声的PMIC或低压差线性稳压器(LDO)为PHY和MAC提供纯净电源,是保证信号完整性和稳定性的关键。设计时需注意模拟与数字电源的隔离。

- 时钟电路

- 需提供高精度的参考时钟(如25MHz、125MHz)给PHY芯片。方案可以是外部独立的晶体振荡器(OSC),或由主控制器提供。时钟的抖动(Jitter)性能直接影响通信质量。

三、 集成电路设计的核心挑战与对策

- 信号完整性(SI)与电磁兼容性(EMC):高速差分信号(如RGMII、SGMII接口)对PCB布板要求极高,需遵循阻抗匹配、等长布线、分层隔离原则。PHY芯片的驱动强度、预加重/去加重设置可用于补偿信道损耗。

- 功耗与散热:尤其是千兆及以上速率,PHY芯片功耗显著增加。设计中需选用低功耗芯片,优化电源设计,并在PCB上考虑散热路径。

- 兼容性与互通性:严格遵循IEEE标准是确保与不同厂商设备互通的基础。设计后期需进行充分的兼容性测试。

四、 典型设计方案示例

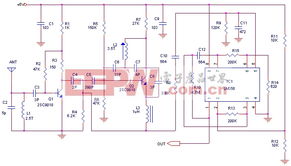

- 低成本嵌入式设备方案:采用集成MAC的ARM Cortex-M系列MCU + 外部单端口10/100M PHY芯片(如LAN8720A)+ HR911105A型集成变压器RJ45插座。接口采用RMII,电路简洁,功耗低。

- 高性能工业网关方案:采用集成MAC的ARM Cortex-A系列MPU(或FPGA-SoC)+ 外部多端口/千兆PHY芯片(如RTL8211F)。接口采用RGMII,配合多层PCB和精密时钟,实现高速可靠通信,可能集成交换或PoE功能。

结论

以太网通信硬件电路的集成电路设计方案,本质上是根据性能、成本、功耗和尺寸要求,对PHY芯片、集成MAC的主控制器、电源及时钟管理等IC进行系统性选型与协同设计的过程。随着技术发展,高度集成化的单芯片SoC方案(集成MAC、PHY乃至交换机)正成为趋势,但理解各分立集成电路模块的设计原理,仍是解决复杂问题、优化系统性能的基础。设计者必须深入理解相关协议标准,并高度重视信号与电源完整性设计,才能实现稳定可靠的以太网通信硬件。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/66.html

更新时间:2026-04-19 02:38:03