语音识别与嵌入式电子电路设计图集锦

语音识别技术作为人机交互的关键接口,正日益广泛应用于智能家居、可穿戴设备、工业控制和消费电子等领域。其核心是将声音信号转化为可处理的数字信号,进而识别和理解语音内容。这一过程离不开精心设计的硬件电路,尤其是嵌入式系统和集成电路的支持。本文将聚焦于语音识别相关的电路设计,特别是嵌入式类电子电路与集成电路的设计要点和图例集锦。

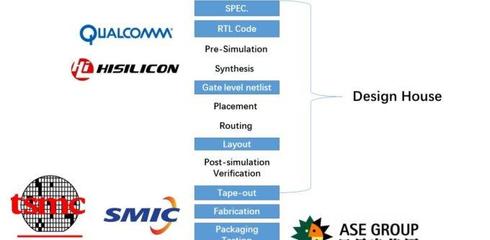

一、语音识别系统的基本硬件架构

一个典型的语音识别硬件系统通常包含以下几个核心部分:麦克风及前置放大电路、模数转换器(ADC)、主控处理单元(通常为微控制器MCU或数字信号处理器DSP)、存储器以及必要的电源管理电路。其信号流程为:声音通过麦克风转换为微弱的模拟电信号,经过前置放大器放大和滤波后,由ADC转换为数字信号,最后交由主控单元进行特征提取和模式识别算法处理。

二、关键电路模块设计图例与解析

- 麦克风输入与前置放大电路

- 驻极体麦克风接口电路:通常需要一个偏置电阻(如2.2kΩ)为麦克风内部的场效应管(FET)提供工作电压,并串联一个耦合电容(如1μF)以隔直流通交流。

- 运算放大器放大电路:采用同相或反相放大结构。例如,使用低噪声运放(如TI的OPA1612)构建增益可调的放大电路,并配合高通滤波器(截止频率约100Hz)滤除环境低频噪声。电路图中需明确显示电阻、电容的取值和运放的供电引脚连接。

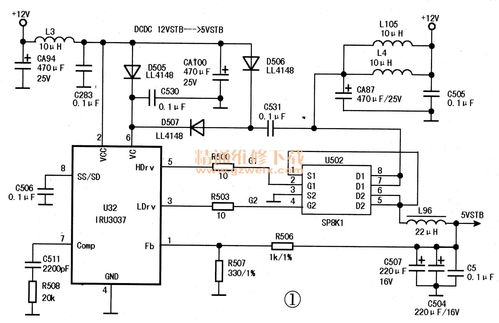

- 模数转换(ADC)电路

- 对于语音信号(带宽通常为300-3400Hz),需选用采样率不低于8kHz的ADC。嵌入式系统中常使用MCU内置的ADC模块。若需外置,可选择Σ-Δ型ADC以获得高信噪比。电路设计需注意模拟电源的滤波,通常在ADC电源引脚附近放置0.1μF和10μF的去耦电容。模拟地与数字地的单点连接也是设计关键,通常在原理图中用磁珠或0Ω电阻标识。

- 主控单元及外围电路

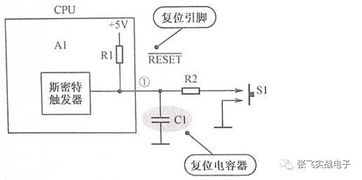

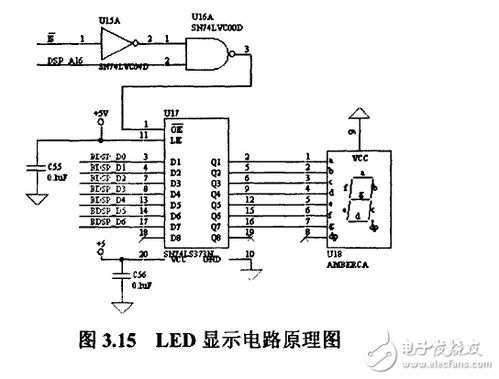

- 以ARM Cortex-M系列MCU(如STM32F4)为核心的嵌入式系统是常见选择。电路图需包含:MCU最小系统(晶体振荡器电路、复位电路、启动模式配置电路)、与ADC的接口(可能是SPI或I2C)、用于存储语音模型的Flash或EEPROM存储器接口电路,以及用于调试的SWD/JTAG接口电路。

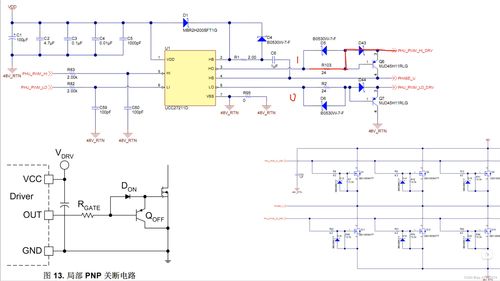

- 电源管理电路:由于语音识别系统可能由电池供电,设计高效的DC-DC降压电路(如使用TI的TPS62740)或低压差线性稳压器(LDO)为模拟和数字部分分别供电,并在原理图中明确标示。

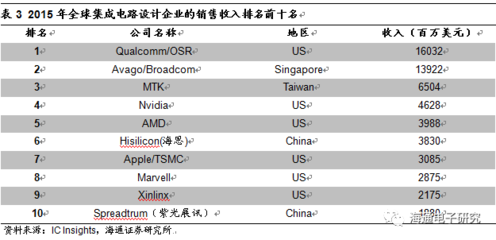

- 专用语音识别集成电路

- 对于低复杂度或始终在线的语音唤醒应用,常采用专用集成电路。例如,科大讯飞的XFS5152芯片或Sensory的Trigger-Speech系列。这些芯片通常集成前置放大器、ADC、语音处理算法和简单的控制接口。设计图需重点展示其典型应用电路:麦克风输入引脚、I2C/SPI/UART与控制MCU的通信线路、电源引脚的去耦设计,以及可能的音频输出电路。

三、嵌入式语音识别电路设计要点

- 低功耗设计:在电路图设计中,需考虑使用功耗低的元器件,并规划电源域,使系统在非活跃时段能进入睡眠模式,仅由语音唤醒电路值守。

- 抗噪声设计:除了电路中的滤波设计,在PCB布局时,模拟信号走线应尽可能短,并用地平面进行屏蔽,远离数字噪声源(如时钟线)。

- 算法与硬件协同:电路设计需与将要运行的语音识别算法(如动态时间规整DTW或深度学习模型)的运算需求相匹配,确保MCU性能、内存和接口资源充足。

四、设计图集锦概览

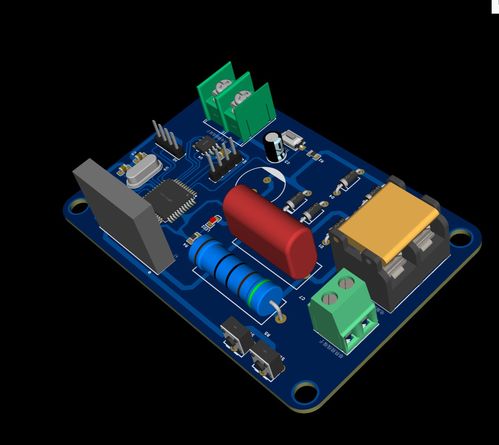

在实际工程中,完整的语音识别嵌入式电路设计图是一套包含原理图、PCB布局图乃至结构框图的文档集合。原理图应层次清晰,模块化绘制;PCB图则需体现良好的电磁兼容性布局。

语音识别电路设计是软硬件结合的典范。从精确的模拟前端到高效的数字处理,再到专用的集成电路方案,每一部分的设计都直接影响识别的准确度和系统的整体效能。工程师在参考现有设计图集时,需深刻理解其原理,并根据具体应用场景(如成本、功耗、识别率要求)进行优化和创新,方能设计出稳定可靠的语音交互硬件平台。

如若转载,请注明出处:http://www.fushanmingchuang.com/product/58.html

更新时间:2026-04-17 00:42:52